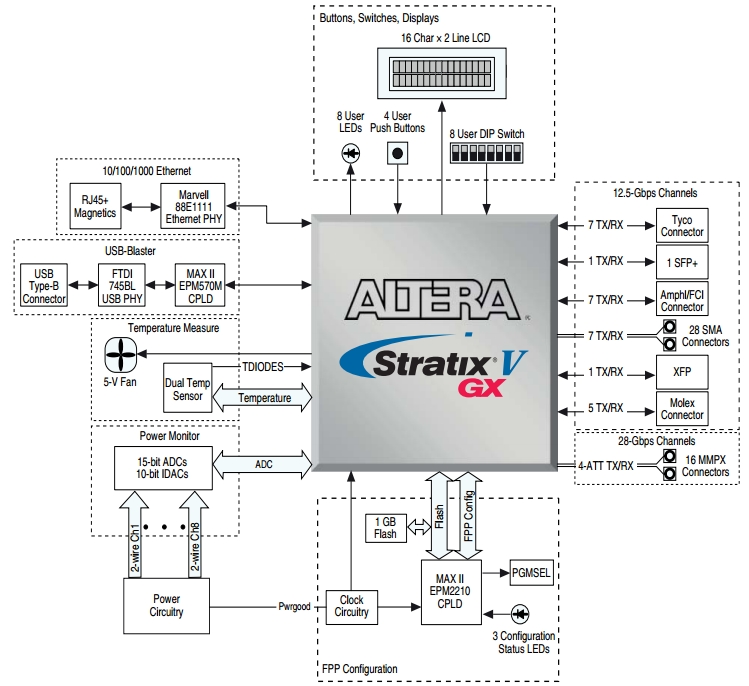

Плата проверки целостности сигналов приемопередатчика ПЛИС FPGA, Stratix V GX Edition

Плата проверки целостности сигналов приемопередатчика Stratix V GX Transceiver Signal Integrity (SI) Development Kit представляет собой платформу для анализа электрических характеристик и функциональной совместимости сигналов приемопередатчиков, реализованных в ПЛИС FPGA компании Altera. Имея доступ к множеству каналов посредством SMA и других стандартных разъемов, разработчик может в реальных условиях протестировать работу многоканальной системы высокоскоростных приемопередатчиков.

Состав отладочного комплекта

- Центральное устройство

- ПЛИС FPGA серии Stratix V GX 5SGXEA7N2F40C2N

- Система конфигурирования

- Конфигурация в режиме Fast Passive Parallel (FPP) посредством ПЛИС CPLD серии MAX II EPM2210 и FLASH памяти

- Интегрированный загрузчик USB-Blaster

- Пользовательские устройства ввода/вывода

- Контроллер Ethernet 10/100/1000 Мбит/с с физическим уровнем (RGMII), с разъемом RJ-45 (медные контакты)

- Алфавитно-цифровой ЖКИ 16х2

- Один 8-позиционный DIP-переключатель

- Четыре пользовательские кнопки

- Устройства памяти

- 128 МБ синхронной FLASH памяти (изначально для хранения конфигурации ПЛИС)

- Компоненты и интерфейсы

- Четыре канала приемопередатчика (TX/RX) на 28 Гбит/с с разъемами MMPX (только для плат версии Stratix V GT)

- Семь каналов приемопередатчика на 12,5 Гбит/с с разъемами SMA

- Один канал приемопередатчика на 12,5 Гбит/с с оптическим SFP+ портом

- Один канал приемопередатчика на 12,5 Гбит/с с оптическим XFP портом

- Пять каналов приемопередатчика на 12,5 Гбит/с с Backplane разъемом компании Molex

- Семь каналов приемопередатчика на 12,5 Гбит/с с Backplane разъемом компании Amphenol

- Семь каналов приемопередатчика на 12,5 Гбит/с с Backplane разъемом компании Tyco

- Разъем USB Type-B

- Разъем RJ-45 для Gigabit Ethernet

- Разъем подключения ЖКИ

- Среда разработки Quartus II, включенная в отладочный комплект

- ПО версии Quartus II Subscription Edition не включено в комплект и не требуется для работы с данной платой

Внутренняя архитектура платы |

Документация:

|